線圈綜合分析儀數(shù)據(jù)處理與存儲支持服務

隨著工業(yè)自動化與檢測技術(shù)的快速發(fā)展,線圈綜合分析儀在電機、變壓器、電磁設備等領域的應用日益廣泛。其數(shù)據(jù)處理與存儲支持服務作為核心功能模塊,直接影響測量結(jié)果的準確性和設備運行的可靠性。本文將系統(tǒng)介紹線圈綜合分析儀數(shù)據(jù)處理與存儲的支持服務內(nèi)容、技術(shù)架構(gòu)及其應用價值。

一、數(shù)據(jù)處理服務

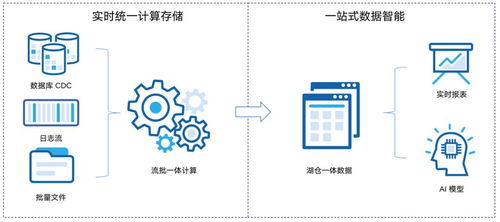

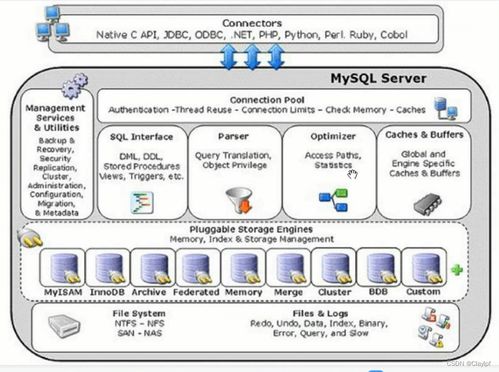

數(shù)據(jù)處理是線圈綜合分析儀的核心環(huán)節(jié),涵蓋信號采集、濾波、計算及分析全過程。通過高精度模數(shù)轉(zhuǎn)換器(ADC)采集線圈的電阻、電感、匝間絕緣等參數(shù),結(jié)合數(shù)字濾波算法去除噪聲干擾,確保原始數(shù)據(jù)的純凈度。隨后,系統(tǒng)依據(jù)預設的電氣模型對數(shù)據(jù)進行實時計算,生成線圈的綜合性能指標,如品質(zhì)因數(shù)(Q值)、損耗角正切(tanδ)等。數(shù)據(jù)分析模塊還支持歷史數(shù)據(jù)對比、趨勢預測及異常診斷,幫助用戶快速識別線圈潛在缺陷,提升維護效率。

二、數(shù)據(jù)存儲支持服務

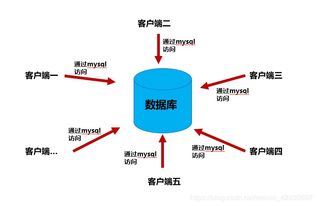

為滿足長期監(jiān)測與追溯需求,線圈綜合分析儀配備多層次數(shù)據(jù)存儲方案。本地存儲采用高速固態(tài)硬盤(SSD),支持實時保存原始數(shù)據(jù)與處理結(jié)果,并提供分類索引功能,便于用戶按時間、設備型號或測試項目快速檢索。同時,系統(tǒng)支持云存儲集成,通過加密傳輸協(xié)議將數(shù)據(jù)同步至遠程服務器,實現(xiàn)多終端訪問與備份,避免因設備故障導致數(shù)據(jù)丟失。數(shù)據(jù)存儲服務還兼容多種格式導出(如CSV、PDF),方便后續(xù)報告生成或第三方軟件分析。

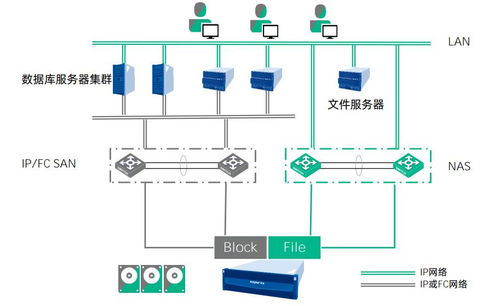

三、技術(shù)架構(gòu)與安全保障

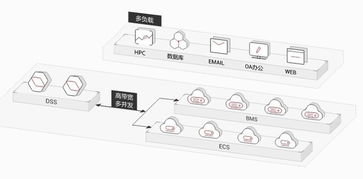

數(shù)據(jù)處理與存儲服務基于嵌入式系統(tǒng)與物聯(lián)網(wǎng)(IoT)技術(shù)構(gòu)建,采用模塊化設計確保擴展性與穩(wěn)定性。核心處理器負責實時運算,而獨立存儲單元通過RAID技術(shù)保障數(shù)據(jù)冗余。在安全方面,系統(tǒng)實施權(quán)限管理機制,限制未授權(quán)訪問,并對敏感數(shù)據(jù)加密存儲。定期自動備份與日志記錄功能進一步增強了數(shù)據(jù)的完整性與可審計性。

四、應用價值與展望

高效的數(shù)據(jù)處理與存儲服務不僅提升了線圈綜合分析儀的測量精度與效率,還為企業(yè)質(zhì)量控制和預測性維護提供了數(shù)據(jù)支撐。未來,隨著人工智能與大數(shù)據(jù)技術(shù)的融合,該服務將進一步強化智能診斷與自適應學習能力,推動工業(yè)檢測向數(shù)字化、智能化方向演進。

線圈綜合分析儀的數(shù)據(jù)處理與存儲支持服務是其技術(shù)先進性的重要體現(xiàn),通過優(yōu)化數(shù)據(jù)流與存儲架構(gòu),為用戶提供可靠、高效的解決方案,助力產(chǎn)業(yè)升級與創(chuàng)新。

如若轉(zhuǎn)載,請注明出處:http://www.fz08.cn/product/11.html

更新時間:2026-04-16 12:32:58